TriCore Instruction Set Architecture

TriCore™ is a unified, 32-bit microcontroller-DSP, single-core architecture optimized for real-time embedded systems. The ISA supports a uniform, 32-bit address space, with optional virtual addressing and memory-mapped I/O. The architecture allows for a wide range of implementations, ranging from scalar through to superscalar, and is capable of interacting with different system architectures, including multiprocessing. This flexibility at the implementation and system levels allows for different trade-offs between performance and cost at any point in time.

The architecture supports both 16-bit and 32-bit instruction formats. All instructions have a 32-bit format. The 16-bit instructions are a subset of the 32-bit instructions, chosen because of their frequency of use. These instructions significantly reduce code space, lowering memory requirements, system and power consumption.

Real-time responsiveness is largely determined by interrupt latency and context-switch time. The high-performance architecture minimizes interrupt latency by avoiding long multi-cycle instructions and by providing a flexible hardware-supported interrupt scheme. The architecture also supports fast-context switching.

History

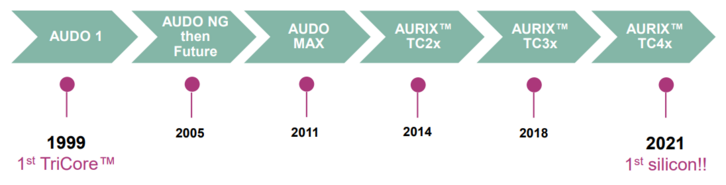

Infineon’s TriCore™ architecture, which underpins the AURIX™ family, has a lineage dating back to the late 1990s. The first TriCore™-based microcontrollers were introduced in 1999 as the Infineon AUDO family (Automotive unified processor), marking the debut of a 32-bit core unifying RISC, microcontroller, and DSP capabilities. Over the next decade, Infineon released several generations of TriCore™-based AUDO MCUs (with increasing performance and integration), establishing a strong presence in automotive powertrain control units. The major breakthrough came in 2012 when Infineon announced the AURIX™ family (the name AURIX™ being an acronym reflecting its automotive real-time focus) as the next evolution of TriCore™ micros. The first-generation AURIX™ (commonly referred to as AURIX TC2xx) featured up to three 32-bit TriCore™ CPUs at 200–300 MHz, with two of the cores optionally arranged in a lockstep pair for safety. These devices, manufactured on a 65 nm process, offered up to about 4–8 MB of flash memory and were among the first automotive MCUs to include a hardware security module for encryption. The AURIX™ TC2xx family quickly became a benchmark for automotive microcontrollers, combining high real-time performance with built-in safety and security, and saw adoption in various vehicle domains from engine management to chassis and ADAS.[2][3][4]

As of January 2022, Infineon has shipped over 845 million TriCore™ devices, including more than 320 million AURIX™ microcontrollers. TriCore™ has proven to be the trusted choice for the automotive industry, with total shipments expected to surpass 1 billion units by the end of 2022. The success story began in the powertrain domain and subsequently expanded to cover the entire automotive MCU market.[1]

The AURIX TC3xx (second-generation AURIX™) was announced in October 2016 as a major upgrade over the first generation, targeting the emerging needs of automated and electric vehicles. While maintaining software and pin compatibility with the TC2xx family, the TC3xx generation doubled the number of cores (scaling up to six TriCore™ cores) and moved to a smaller geometry 40 nm process to integrate larger memories and new peripherals. Key improvements introduced with TC3xx included: higher total processing performance (achieving 3× the real-time computing capability of its predecessor), increased on-chip flash (up to 16 MB) and SRAM (>6 MB) to accommodate the growing software in vehicles, a enhanced HSM with full EVITA support for cybersecurity, and new connectivity options like Gigabit Ethernet and more CAN FD channels to handle the data fusion requirements of ADAS. The TC3xx also introduced dedicated radar processing units (SPUs) to support level 2+ and level 3 autonomous driving systems that process radar sensor data on the MCU. Engineering samples of the flagship 300 MHz, 6-core TC39x became available in 2017, and the family entered volume production by 2019 once it achieved full automotive qualification. The seamless backward compatibility eased the migration for automakers and Tier-1 suppliers, allowing them to leverage existing AURIX™ TC2xx software and safety concepts on the more powerful TC3xx platform.[5][6][7]

As of the mid-2020s, Infineon has continued to evolve the AURIX™ lineage. In 2023, the company revealed the third-generation AURIX TC4x family, representing the 7th generation of TriCore™-based MCUs overall. The TC4x family (in development) is slated to bring further enhancements such as higher CPU frequencies, larger local memories, an enhanced TriCore™ core design with improved floating-point and virtualization support, and even the integration of auxiliary cores (including potentially heterogeneous cores). Notably, Infineon is also embracing emerging technology by planning to incorporate RISC-V processor cores alongside TriCore™ in future AURIX™ products, combining the proven safety of TriCore™ with the flexibility of the open RISC-V ecosystem. Throughout its history, the AURIX™ architecture’s roadmap has been driven by the increasing computational demands and safety requirements of modern vehicles – from the early single-core engine controllers to today’s multi-core domain controllers for autonomous driving. Each generation has built upon the last, adding more performance, memory, and features while preserving the fundamental focus on real-time determinism, safety, and security that the TriCore™ architecture was originally created for. [2][8]

As of January 2022, Infineon has shipped over 845 million TriCore™ devices, including more than 320 million AURIX™ microcontrollers. TriCore™ has proven to be the trusted choice for the automotive industry, with total shipments expected to surpass 1 billion units by the end of 2022. The success story began in the powertrain domain and subsequently expanded to cover the entire automotive MCU market.[1]

Versions

| ISA | Processors | User Manual Date | New Instructions |

|---|---|---|---|

| TC1.3 | 2002-05 | ||

| TC1.3.1 | TriCore™ Family AUDO MAX | 2007-11 |

|

| TC1.6 | Infineon AURIX TC2xx | 2013-07 |

|

| TC1.6.2 | Infineon AURIX TC3xx | 2017-01 |

|

| TC1.8 | Infineon AURIX TC4x | N/A | N/A (user manual not yet public available) |

Features

The key features of the TriCore™ Instruction Set Architecture (ISA) are:

- 32-bit load store architecture

- 4 Gbyte address range (232)

- 16-bit and 32-bit instructions for reduced code size

- Data types:

- Boolean, integer with saturation, bit array, signed fraction, character, double-word integers, signed integer, unsigned integer, IEEE-754 single-precision floating point

- Data formats:

- Bit, byte (8-bits), half-word (16-bits), word (32-bits), double-word (64-bits)

- Byte and bit addressing

- Little-endian byte ordering for data, memory and CPU registers

- Multiply and Accumulate (MAC) instructions: Dual 16 × 16, 16 × 32, 32 × 32

- Saturation integer arithmetic

- Packed data

- Addressing modes:

- Absolute, circular, bit reverse, long + short, base + offset with pre- and post-update

- Instruction types:

- Arithmetic, address arithmetic, comparison, address comparison, logical, MAC, shift, coprocessor, bit logical, branch, bit field, load/store, packed data, system

- General Purpose Register Set (GPRS):

- Sixteen 32-bit data registers

- Sixteen 32-bit address registers

- Three 32-bit status and program counter registers (PSW, PC, PCXI)

- Debug support (OCDS):

- Level 1, supported in conjunction with the CPS block

- Level 3, supported in conjunction with the MCDS block (Emulation Device only).

- Flexible memory protection system providing multiple protection sets with multiple protection ranges per set.

- Temporal protection system allowing time bounded real time operation

Register Set

Architectural Registers

The architectural registers consist of:

- 32 General Purpose Registers (GPRs)

- 16 Address Registers

- 16 Data Registers

- Program Counter (PC)

- Two 32-bit registers containing status flags

|

|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Special Registers

| General Special Registers | |

|---|---|

| PC | Program Counter Register |

| SYSCON | System Configuration Register |

| CPU_ID | CPU Identification Register (Read Only) |

| CORE_ID | Core Identification Register |

| BIV | Base Address of Interrupt Vector Table Register |

| BTV | Base Address of Trap Vector Table Register |

| ISP | Interrupt Stack Pointer Register |

| ICR | ICU Interrupt Control Register |

| FCX | Free Context List Head Pointer Register |

| LCX | Free Context List Limit Pointer Register |

| COMPAT | Compatibility Mode Register |

| Debug Registers | |

|---|---|

| DBGSR | Debug Status Register |

| EXEVT | External Event Register |

| CREVT | Core Register Event Register |

| SWEVT | Software Event Register |

| TR0EVT | Trigger Event 0 Register |

| TR0ADR | Trigger Address 0 Register |

| ⋮ | |

| TR7EVT | Trigger Event 7 Register |

| TR7ADR | Trigger Address 7 Register |

| TRIG_ACC | Trigger Accumulator Register |

| DMS | Debug Monitor Start Address Register |

| DCX | Debug Context Save Address Register |

| TASK_ASI | TASK Address Space Identifier Register |

| DBGTCR | Debug Trap Control Register |

| CCTRL | Counter Control Register |

| CCNT | CPU Clock Count Register |

| ICNT | Instruction Count Register |

| M1CNT | Multi Count Register 1 |

| M2CNT | Multi Count Register 2 |

| M3CNT | Multi Count Register 3 |

| Floating Point Registers | |

|---|---|

| FPU_TRAP_CON | Trap Control Register |

| FPU_TRAP_PC | Trapping Instruction Program Control Register |

| FPU_TRAP_OPC | Trapping Instruction Opcode Register |

| FPU_TRAP_SRC1 | Trapping Instruction SRC1 Operand Register |

| FPU_TRAP_SRC2 | Trapping Instruction SRC2 Operand Register |

| FPU_TRAP_SRC3 | Trapping Instruction SRC3 Operand Register |

Instructions Set

Pipeline

| Acronym | Pipeline |

|---|---|

| LS | Load/Store |

| IP | Integer Pipeline |

| FPU | Floating Point Unit |

Classes

| Class | Pipeline | Description | Example |

|---|---|---|---|

| Arithmetic | LS | Arithmetic operations involving addresses. | ADD.A, ADDIH.A |

| Arithmetic | IP | Arithmetic operations involving integers. | ADD, SUB |

| Cache | LS | Cache management operations. | CACHEA.W, CACHEA.WI |

| Compare | IP | Comparison operations. | EQ, GE |

| Control Flow | LS | Control flow instructions for branching. | J, JNE.A |

| Control Flow | IP | Control flow operations for branching. | JEQ, JLT |

| Coprocessor 0 | IP | Special operations using coprocessor 0. | CRC32.B, IXMAX |

| Count | IP | Counting bits in registers. | CLO, CLZ |

| CSA Control Flow | LS | Context Save Areas (CSA) control flow instructions | CALL, BISR |

| Extract | IP | Bit field extraction and manipulation. | DEXTR, INS.T |

| Floating Point | FPU | Floating-point instructions | ADDF, SUBF |

| Integer Divide | IP | Integer division operations. | DIV, DVSTEP |

| Load | LS | Load data from memory. | LD.A, LDUCX |

| Logical | IP | Bitwise logical operations. | AND, OR |

| Move | LS | Move data between registers. | MOV.A, MOV.AA |

| Move | IP | Move operations with conditions. | CMOV, MOV |

| Multiply | IP | Multiplication operations. | MUL, MULS |

| Multiply Accumulate | IP | Multiply and accumulate operations. | MADD, MSUB |

| Shift | IP | Bit shift operations. | SH, SHA |

| Store | LS | Store data to memory. | ST.A, ST.B |

| Sync | LS | Synchronization operations. | DSYNC, ISYNC |

| Trap and Interrupt | LS | Interrupt and trap operations. | DEBUG, TRAPV |

Instruction List

| Pipeline | Class | Mnemonic | Longname | ISA Version |

|---|---|---|---|---|

| LS | Arithmetic | ADD.A | Add Address | |

| LS | Arithmetic | ADDIH.A | Add Immediate High to Address | |

| LS | Arithmetic | ADDSC.A | Add Scaled Index to Address | |

| LS | Arithmetic | ADDSC.AT | Add Bit-Scaled Index to Address | |

| LS | CSA Control Flow | BISR | Begin Interrupt Service Routine | |

| LS | Cache | CACHEA.I | Cache Address, Invalidate | |

| LS | Cache | CACHEA.W | Cache Address, Writeback | TC1.3.1 |

| LS | Cache | CACHEA.WI | Cache Address, Writeback and Invalidate | TC1.3.1 |

| LS | Cache | CACHEI.W | Cache Index, Writeback | |

| LS | Cache | CACHEI.I | Cache Index, Invalidate | TC1.6 |

| LS | Cache | CACHEI.WI | Cache Index, Writeback, Invalidate | |

| LS | CSA Control Flow | CALL | Call | |

| LS | CSA Control Flow | CALLA | Call Absolute | |

| LS | CSA Control Flow | CALLI | Call Indirect | |

| LS | Load | CMPSWAP.W | Compare and Swap | TC1.6 |

| LS | Trap and Interrupt | DEBUG | Debug | |

| LS | Trap and Interrupt | DISABLE | Disable Interrupts | TC1.6 |

| LS | Sync | DSYNC | Synchronize Data | |

| LS | Trap and Interrupt | ENABLE | Enable Interrupts | |

| LS | Arithmetic | EQ.A | Equal to Address | |

| LS | Arithmetic | EQZ.A | Equal Zero Address | |

| LS | CSA Control Flow | FCALL | Fast Call | TC1.6 |

| LS | CSA Control Flow | FCALLA | Fast Call Absolute | TC1.6 |

| LS | CSA Control Flow | FCALLI | Fast Call Indirect | TC1.6 |

| LS | CSA Control Flow | FRET | Return from Fast Call | TC1.6 |

| LS | Arithmetic | GE.A | Greater Than or Equal Address | |

| LS | Sync | ISYNC | Synchronize Instructions | |

| LS | Control Flow | J | Jump Unconditional | |

| LS | Control Flow | JA | Jump Unconditional Absolute | |

| LS | Control Flow | JEQ.A | Jump if Equal Address | |

| LS | Control Flow | JI | Jump Indirect | |

| LS | Control Flow | JL | Jump and Link | |

| LS | Control Flow | JLA | Jump and Link Absolute | |

| LS | Control Flow | JLI | Jump and Link Indirect | |

| LS | Control Flow | JNE.A | Jump if Not Equal Address | |

| LS | Control Flow | JNZ.A | Jump if Not Equal to Zero Address | |

| LS | Control Flow | JZ.A | Jump if Zero Address | |

| LS | Load | LD.A | Load Word to Address Register | |

| LS | Load | LD.B | Load Byte | TC1.6* |

| LS | Load | LD.BU | Load Byte Unsigned | TC1.6* |

| LS | Load | LD.D | Load Double-word | |

| LS | Load | LD.DA | Load Double-word to Address Register | |

| LS | Load | LD.H | Load Half-word | TC1.6* |

| LS | Load | LD.HU | Load Half-word Unsigned | TC1.6* |

| LS | Load | LD.Q | Load Half-word Signed Fraction | |

| LS | Load | LD.W | Load Word | |

| LS | Load | LDLCX | Load Lower Context | |

| LS | Store | LDMST | Load-Modify-Store | |

| LS | Load | LDUCX | Load Upper Context | |

| LS | Load | LEA | Load Effective Address | |

| LS | Load | LHA | Load High Address | TC1.6.2 |

| LS | Control Flow | LOOP | Loop | |

| LS | Control Flow | LOOPU | Loop Unconditional | |

| LS | Arithmetic | LT.A | Less Than Address | |

| LS | Move | MFCR | Move From Core Register | |

| LS | Move | MOV.A | Move Value to Address Register | |

| LS | Move | MOV.AA | Move Address from Address Register | |

| LS | Move | MOV.D | Move Address to Data Register | |

| LS | Move | MOVH.A | Move High to Address | |

| LS | Move | MTCR | Move To Core Register | |

| LS | Arithmetic | NE.A | Not Equal Address | |

| LS | Arithmetic | NEZ.A | Not Equal Zero Address | |

| LS | Arithmetic | NOP | No Operation | |

| LS | Trap and Interrupt | RESTORE | Restore | TC1.6 |

| LS | CSA Control Flow | RET | Return from Call | |

| LS | CSA Control Flow | RFE | Return From Exception | |

| LS | CSA Control Flow | RFM | Return From Monitor | |

| LS | CSA Control Flow | RSLCX | Restore Lower Context | |

| LS | Store | ST.A | Store Word from Address Register | TC1.6* |

| LS | Store | ST.B | Store Byte | TC1.6* |

| LS | Store | ST.D | Store Double-word | |

| LS | Store | ST.DA | Store Double-word from Address Registers | |

| LS | Store | ST.H | Store Half-word | TC1.6* |

| LS | Store | ST.Q | Store Half-word Signed Fraction | |

| LS | Store | ST.T | Store Bit | |

| LS | Store | ST.W | Store Word | |

| LS | Store | STLCX | Store Lower Context | |

| LS | Store | STUCX | Store Upper Context | |

| LS | Arithmetic | SUB.A | Subtract Address | |

| LS | CSA Control Flow | SVLCX | Save Lower Context | |

| LS | Load | SWAP.W | Swap with Data Register | |

| LS | Load | SWAPMSK.W | Swap under Mask | TC1.6 |

| LS | CSA Control Flow | SYSCALL | System Call | |

| LS | Trap and Interrupt | TRAPSV | Trap on Sticky Overflow | |

| LS | Trap and Interrupt | TRAPV | Trap on Overflow | |

| LS | Trap and Interrupt | WAIT | Wait | TC1.6 |

| IP | Arithmetic | ABS | Absolute Value | |

| IP | Arithmetic | ABS.B | Absolute Value Packed Byte | |

| IP | Arithmetic | ABS.H | Absolute Value Packed Half-word | |

| IP | Arithmetic | ABSDIF | Absolute Value of Difference | |

| IP | Arithmetic | ABSDIF.B | Absolute Value of Difference Packed Byte | |

| IP | Arithmetic | ABSDIF.H | Absolute Value of Difference Packed Half-word | |

| IP | Arithmetic | ABSDIFS | Absolute Value of Difference with Saturation | |

| IP | Arithmetic | ABSDIFS.H | Absolute Value of Difference Packed Half-word with Saturation | |

| IP | Arithmetic | ABSS | Absolute Value with Saturation | |

| IP | Arithmetic | ABSS.H | Absolute Value Packed Half-word with Saturation | |

| IP | Arithmetic | ADD | Add | |

| IP | Arithmetic | ADD.B | Add Packed Byte | |

| IP | Arithmetic | ADD.H | Add Packed Half-word | |

| IP | Arithmetic | ADDC | Add with Carry | |

| IP | Arithmetic | ADDI | Add Immediate | |

| IP | Arithmetic | ADDIH | Add Immediate High | |

| IP | Arithmetic | ADDS | Add Signed with Saturation | |

| IP | Arithmetic | ADDS.H | Add Signed Packed Half-word with Saturation | |

| IP | Arithmetic | ADDS.HU | Add Unsigned Packed Half-word with Saturation | |

| IP | Arithmetic | ADDS.U | Add Unsigned with Saturation | |

| IP | Arithmetic | ADDX | Add Extended | |

| IP | Logical | AND | Bitwise AND | |

| IP | Logical | AND.AND.T | Accumulating Bit Logical AND-AND | |

| IP | Logical | AND.ANDN.T | Accumulating Bit Logical AND-AND-Not | |

| IP | Logical | AND.NOR.T | Accumulating Bit Logical AND-NOR | |

| IP | Logical | AND.OR.T | Accumulating Bit Logical AND-OR | |

| IP | Logical | AND.EQ | Equal Accumulating | |

| IP | Logical | AND.GE | Greater Than or Equal Accumulating | |

| IP | Logical | AND.GE.U | Greater Than or Equal Accumulating Unsigned | |

| IP | Logical | AND.LT | Less Than Accumulating | |

| IP | Logical | AND.LT.U | Less Than Accumulating Unsigned | |

| IP | Logical | AND.NE | Not Equal Accumulating | |

| IP | Logical | AND.T | Bit Logical AND | |

| IP | Logical | ANDN | Bitwise AND-Not | |

| IP | Logical | ANDN.T | Bit Logical AND-Not | |

| IP | Coprocessor 0 | BMERGE | Bit Merge | |

| IP | Coprocessor 0 | BSPLIT | Bit Split | |

| IP | Arithmetic | CADD | Conditional Add | |

| IP | Arithmetic | CADDN | Conditional Add-Not | |

| IP | Count | CLO | Count Leading Ones | |

| IP | Count | CLO.H | Count Leading Ones in Packed Half-words | |

| IP | Count | CLS | Count Leading Signs | |

| IP | Count | CLS.H | Count Leading Signs in Packed Half-words | |

| IP | Count | CLZ | Count Leading Zeros | |

| IP | Count | CLZ.H | Count Leading Zeros in Packed Half-words | |

| IP | Move | CMOV (16-bit) | Conditional Move (16-bit) | |

| IP | Move | CMOVN (16-bit) | Conditional Move-Not (16-bit) | |

| IP | Coprocessor 0 | CRC32.B | CRC32 Byte | TC1.6.2 |

| IP | Coprocessor 0 | CRC32B.W CRC32 (TC1.6) | CRC32 Word Big-Endian | TC1.6 |

| IP | Coprocessor 0 | CRC32L.W | CRC32 Word Little-Endian | TC1.6.2 |

| IP | Coprocessor 0 | CRCN | User-Defined CRC | TC1.6.2 |

| IP | Arithmetic | CSUB | Conditional Subtract | |

| IP | Arithmetic | CSUBN | Conditional Subtract-Not | |

| IP | Extract | DEXTR | Extract from Double Register | |

| IP | Integer Divide | DVADJ | Divide-Adjust | |

| IP | Integer Divide | DIV | Divide | TC1.6 |

| IP | Integer Divide | DIV.U | Divide Unsigned | TC1.6 |

| IP | Integer Divide | DVINIT | Divide-Initialization Word | |

| IP | Integer Divide | DVINIT.U | Divide-Initialization Word Unsigned | |

| IP | Integer Divide | DVINIT.B | Divide-Initialization Byte | |

| IP | Integer Divide | DVINIT.BU | Divide-Initialization Byte Unsigned | |

| IP | Integer Divide | DVINIT.H | Divide-Initialization Half-word | |

| IP | Integer Divide | DVINIT.HU | Divide-Initialization Half-word Unsigned | |

| IP | Integer Divide | DVSTEP | Divide-Step | |

| IP | Integer Divide | DVSTEP.U | Divide-Step Unsigned | |

| IP | Compare | EQ | Equal | |

| IP | Compare | EQ.B | Equal Packed Byte | |

| IP | Compare | EQ.H | Equal Packed Half-word | |

| IP | Compare | EQ.W | Equal Packed Word | |

| IP | Compare | EQANY.B | Equal Any Byte | |

| IP | Compare | EQANY.H | Equal Any Half-word | |

| IP | Extract | EXTR | Extract Bit Field | |

| IP | Extract | EXTR.U | Extract Bit Field Unsigned | |

| IP | Compare | GE | Greater Than or Equal | |

| IP | Compare | GE.U | Greater Than or Equal Unsigned | |

| IP | Extract | IMASK | Insert Mask | |

| IP | Extract | INS.T | Insert Bit | |

| IP | Extract | INSN.T | Insert Bit-Not | |

| IP | Extract | INSERT | Insert Bit Field | |

| IP | Coprocessor 0 | IXMAX | Find Maximum Index | |

| IP | Coprocessor 0 | IXMAX.U | Find Maximum Index (unsigned) | |

| IP | Coprocessor 0 | IXMIN | Find Minimum Index | |

| IP | Coprocessor 0 | IXMIN.U | Find Minimum Index (unsigned) | |

| IP | Control Flow | JEQ | Jump if Equal | TC1.6* |

| IP | Control Flow | JGE | Jump if Greater Than or Equal | |

| IP | Control Flow | JGE.U | Jump if Greater Than or Equal Unsigned | |

| IP | Control Flow | JGEZ (16-bit) | Jump if Greater Than or Equal to Zero (16-bit) | |

| IP | Control Flow | JGTZ (16-bit) | Jump if Greater Than Zero (16-bit) | |

| IP | Control Flow | JLEZ (16-bit) | Jump if Less Than or Equal to Zero (16-bit) | |

| IP | Control Flow | JLT | Jump if Less Than | |

| IP | Control Flow | JLT.U | Jump if Less Than Unsigned | |

| IP | Control Flow | JLTZ (16-bit) | Jump if Less Than Zero (16-bit) | |

| IP | Control Flow | JNE | Jump if Not Equal | TC1.6* |

| IP | Control Flow | JNED | Jump if Not Equal and Decrement | |

| IP | Control Flow | JNEI | Jump if Not Equal and Increment | |

| IP | Control Flow | JNZ (16-bit) | Jump if Not Equal to Zero (16-bit) | |

| IP | Control Flow | JNZ.T | Jump if Not Equal to Zero Bit | |

| IP | Control Flow | JZ (16-bit) | Jump if Zero (16-bit) | |

| IP | Control Flow | JZ.T | Jump if Zero Bit | |

| IP | Compare | LT | Less Than | |

| IP | Compare | LT.U | Less Than Unsigned | |

| IP | Compare | LT.B | Less Than Packed Byte | |

| IP | Compare | LT.BU | Less Than Packed Byte Unsigned | |

| IP | Compare | LT.H | Less Than Packed Half-word | |

| IP | Compare | LT.HU | Less Than Packed Half-word Unsigned | |

| IP | Compare | LT.W | Less Than Packed Word | |

| IP | Compare | LT.WU | Less Than Packed Word Unsigned | |

| IP | Multiply Accumulate | MADD | Multiply-Add | |

| IP | Multiply Accumulate | MADDS | Multiply-Add, Saturated | |

| IP | Multiply Accumulate | MADD.H | Packed Multiply-Add Q Format | |

| IP | Multiply Accumulate | MADDS.H | Packed Multiply-Add Q Format, Saturated | |

| IP | Multiply Accumulate | MADD.Q | Multiply-Add Q Format | |

| IP | Multiply Accumulate | MADDS.Q | Multiply-Add Q Format, Saturated | |

| IP | Multiply Accumulate | MADD.U | Multiply-Add Unsigned | |

| IP | Multiply Accumulate | MADDS.U | Multiply-Add Unsigned, Saturated | |

| IP | Multiply Accumulate | MADDM.H | Packed Multiply-Add Q Format Multi-precision | |

| IP | Multiply Accumulate | MADDMS.H | Packed Multiply-Add Q Format Multi-precision, Saturated | |

| IP | Multiply Accumulate | MADDR.H | Packed Multiply-Add Q Format with Rounding | |

| IP | Multiply Accumulate | MADDRS.H | Packed Multiply-Add Q Format with Rounding, Saturated | |

| IP | Multiply Accumulate | MADDR.Q | Multiply-Add Q Format with Rounding | |

| IP | Multiply Accumulate | MADDRS.Q | Multiply-Add Q Format with Rounding, Saturated | |

| IP | Multiply Accumulate | MADDSU.H | Packed Multiply-Add/Subtract Q Format | |

| IP | Multiply Accumulate | MADDSUS.H | Packed Multiply-Add/Subtract Q Format Saturated | |

| IP | Multiply Accumulate | MADDSUM.H | Packed Multiply-Add/Subtract Q Format Multi-precision | |

| IP | Multiply Accumulate | MADDSUMS.H | Packed Multiply-Add/Subtract Q Format Multi-precision Saturated | |

| IP | Multiply Accumulate | MADDSUR.H | Packed Multiply-Add/Subtract Q Format with Rounding | |

| IP | Multiply Accumulate | MADDSURS.H | Packed Multiply-Add/Subtract Q Format with Rounding Saturated | |

| IP | Arithmetic | MAX | Maximum Value | |

| IP | Arithmetic | MAX.U | Maximum Value Unsigned | |

| IP | Arithmetic | MAX.B | Maximum Value Packed Byte | |

| IP | Arithmetic | MAX.BU | Maximum Value Packed Byte Unsigned | |

| IP | Arithmetic | MAX.H | Maximum Value Packed Half-word | |

| IP | Arithmetic | MAX.HU | Maximum Value Packed Half-word Unsigned | |

| IP | Arithmetic | MIN | Minimum Value | |

| IP | Arithmetic | MIN.U | Minimum Value Unsigned | |

| IP | Arithmetic | MIN.B | Minimum Value Packed Byte | |

| IP | Arithmetic | MIN.BU | Minimum Value Packed Byte Unsigned | |

| IP | Arithmetic | MIN.H | Minimum Value Packed Half-word | |

| IP | Arithmetic | MIN.HU | Minimum Value Packed Half-word Unsigned | |

| IP | Move | MOV | Move | |

| IP | Move | MOV.U | Move Unsigned | |

| IP | Move | MOVH | Move High | |

| IP | Multiply Accumulate | MSUB | Multiply-Subtract | |

| IP | Multiply Accumulate | MSUBS | Multiply-Subtract, Saturated | |

| IP | Multiply Accumulate | MSUB.H | Packed Multiply-Subtract Q Format | |

| IP | Multiply Accumulate | MSUBS.H | Packed Multiply-Subtract Q Format, Saturated | |

| IP | Multiply Accumulate | MSUB.Q | Multiply-Subtract Q Format | |

| IP | Multiply Accumulate | MSUBS.Q | Multiply-Subtract Q Format, Saturated | |

| IP | Multiply Accumulate | MSUB.U | Multiply-Subtract Unsigned | |

| IP | Multiply Accumulate | MSUBS.U | Multiply-Subtract Unsigned, Saturated | |

| IP | Multiply Accumulate | MSUBAD.H | Packed Multiply-Subtract/Add Q Format | |

| IP | Multiply Accumulate | MSUBADS.H | Packed Multiply-Subtract/Add Q Format, Saturated | |

| IP | Multiply Accumulate | MSUBADM.H | Packed Multiply-Subtract/Add Q Format-Multi-precision | |

| IP | Multiply Accumulate | MSUBADMS.H | Packed Multiply-Subtract/Add Q Format-Multi-precision, Saturated | |

| IP | Multiply Accumulate | MSUBADR.H | Packed Multiply-Subtract/Add Q Format with Rounding | |

| IP | Multiply Accumulate | MSUBADRS.H | Packed Multiply-Subtract/Add Q Format with Rounding, Saturated | |

| IP | Multiply Accumulate | MSUBM.H | Packed Multiply-Subtract Q Format-Multi-precision | |

| IP | Multiply Accumulate | MSUBMS.H | Packed Multiply-Subtract Q Format-Multi-precision, Saturated | |

| IP | Multiply Accumulate | MSUBR.H | Packed Multiply-Subtract Q Format with Rounding | |

| IP | Multiply Accumulate | MSUBRS.H | Packed Multiply-Subtract Q Format with Rounding, Saturated | |

| IP | Multiply Accumulate | MSUBR.Q | Multiply-Subtract Q Format with Rounding | |

| IP | Multiply Accumulate | MSUBRS.Q | Multiply-Subtract Q Format with Rounding, Saturated | |

| IP | Multiply | MUL | Multiply | |

| IP | Multiply | MULS | Multiply, Saturated | |

| IP | Multiply | MUL.H | Packed Multiply Q Format | |

| IP | Multiply | MUL.Q | Multiply Q Format | |

| IP | Multiply | MUL.U | Multiply Unsigned | |

| IP | Multiply | MULS.U | Multiply Unsigned, Saturated | |

| IP | Multiply | MULM.H | Packed Multiply Q Format-Multi-precision | |

| IP | Multiply | MULR.H | Packed Multiply Q Format with Rounding | |

| IP | Multiply | MULR.Q | Multiply Q Format with Rounding | |

| IP | Logical | NAND | Bitwise NAND | |

| IP | Logical | NAND.T | Bit Logical NAND | |

| IP | Compare | NE | Not Equal | |

| IP | Logical | NOR | Bitwise NOR | |

| IP | Logical | NOR.T | Bit Logical NOR | |

| IP | Logical | NOT (16-bit) | Bitwise Complement NOT (16-bit) | |

| IP | Logical | OR | Bitwise OR | |

| IP | Logical | OR.AND.T | Accumulating Bit Logical OR-AND | |

| IP | Logical | OR.ANDN.T | Accumulating Bit Logical OR-AND-Not | |

| IP | Logical | OR.NOR.T | Accumulating Bit Logical OR-NOR | |

| IP | Logical | OR.OR.T | Accumulating Bit Logical OR-OR | |

| IP | Logical | OR.EQ | Equal Accumulating | |

| IP | Logical | OR.GE | Greater Than or Equal Accumulating | |

| IP | Logical | OR.GE.U | Greater Than or Equal Accumulating Unsigned | |

| IP | Logical | OR.LT | Less Than Accumulating | |

| IP | Logical | OR.LT.U | Less Than Accumulating Unsigned | |

| IP | Logical | OR.NE | Not Equal Accumulating | |

| IP | Logical | OR.T | Bit Logical OR | |

| IP | Logical | ORN | Bitwise OR-Not | |

| IP | Logical | ORN.T | Bit Logical OR-Not | |

| IP | Coprocessor 0 | PACK | Pack | |

| IP | Coprocessor 0 | PARITY | Parity | |

| IP | Count | POPCNT.W | Population Count Word | TC1.6.2 |

| IP | Trap and Interrupt | RSTV | Reset Overflow Bits | |

| IP | Arithmetic | RSUB | Reverse-Subtract | |

| IP | Arithmetic | RSUBS | Reverse-Subtract with Saturation | |

| IP | Arithmetic | RSUBS.U | Reverse-Subtract Unsigned with Saturation | |

| IP | Arithmetic | SAT.B | Saturate Byte | |

| IP | Arithmetic | SAT.BU | Saturate Byte Unsigned | |

| IP | Arithmetic | SAT.H | Saturate Half-word | |

| IP | Arithmetic | SAT.HU | Saturate Half-word Unsigned | |

| IP | Arithmetic | SEL | Select | |

| IP | Arithmetic | SELN | Select-Not | |

| IP | Shift | SH | Shift | |

| IP | Shift | SH.EQ | Shift Equal | |

| IP | Shift | SH.GE | Shift Greater Than or Equal | |

| IP | Shift | SH.GE.U | Shift Greater Than or Equal Unsigned | |

| IP | Shift | SH.H | Shift Packed Half-words | |

| IP | Shift | SH.LT | Shift Less Than | |

| IP | Shift | SH.LT.U | Shift Less Than Unsigned | |

| IP | Shift | SH.NE | Shift Not Equal | |

| IP | Shift | SH.AND.T | Accumulating Shift-AND | |

| IP | Shift | SH.ANDN.T | Accumulating Shift-AND-Not | |

| IP | Shift | SH.NAND.T | Accumulating Shift-NAND | |

| IP | Shift | SH.NOR.T | Accumulating Shift-NOR | |

| IP | Shift | SH.OR.T | Accumulating Shift-OR | |

| IP | Shift | SH.ORN.T | Accumulating Shift-OR-Not | |

| IP | Shift | SH.XNOR.T | Accumulating Shift-XNOR | |

| IP | Shift | SH.XOR.T | Accumulating Shift-XOR | |

| IP | Shift | SHA | Arithmetic Shift | |

| IP | Shift | SHA.H | Arithmetic Shift Packed Half-words | |

| IP | Shift | SHAS | Arithmetic Shift with Saturation | |

| IP | Arithmetic | SHUFFLE | Byte Shuffle | TC1.6.2 |

| IP | Arithmetic | SUB | Subtract | |

| IP | Arithmetic | SUB.B | Subtract Packed Byte | |

| IP | Arithmetic | SUB.H | Subtract Packed Half-word | |

| IP | Arithmetic | SUBC | Subtract With Carry | |

| IP | Arithmetic | SUBS | Subtract Signed with Saturation | |

| IP | Arithmetic | SUBS.U | Subtract Unsigned with Saturation | |

| IP | Arithmetic | SUBS.H | Subtract Packed Half-word with Saturation | |

| IP | Arithmetic | SUBS.HU | Subtract Packed Half-word Unsigned with Saturation | |

| IP | Arithmetic | SUBX | Subtract Extended | |

| IP | Coprocessor 0 | UNPACK | Unpack Floating Point | |

| IP | Logical | XNOR | Bitwise XNOR | |

| IP | Logical | XNOR.T | Bit Logical XNOR | |

| IP | Logical | XOR | Bitwise XOR | |

| IP | Logical | XOR.EQ | Equal Accumulating | |

| IP | Logical | XOR.GE | Greater Than or Equal Accumulating | |

| IP | Logical | XOR.GE.U | Greater Than or Equal Accumulating Unsigned | |

| IP | Logical | XOR.LT | Less Than Accumulating | |

| IP | Logical | XOR.LT.U | Less Than Accumulating Unsigned | |

| IP | Logical | XOR.NE | Not Equal Accumulating | |

| IP | Logical | XOR.T | Bit Logical XOR | |

| FPU | Floating Point | ADD.F | Add Float | |

| FPU | Floating Point | CMP.F | Compare Float | |

| FPU | Floating Point | DIV.F | Divide Float | |

| FPU | Floating Point | FTOI | Float to Integer | |

| FPU | Floating Point | FTOIZ | Float to Integer, Round towards Zero | TC1.3.1 |

| FPU | Floating Point | FTOQ31 | Float to Fraction | |

| FPU | Floating Point | FTOQ31Z | Float to Fraction, Round towards Zero | TC1.3.1 |

| FPU | Floating Point | FTOU | Float to Unsigned | |

| FPU | Floating Point | FTOUZ | Float to Unsigned, Round towards Zero | TC1.3.1 |

| FPU | Floating Point | FTOHP | Single Precision to Half Precision | TC1.6.2 |

| FPU | Floating Point | HPTOF | Half Precision to Single Precision | TC1.6.2 |

| FPU | Floating Point | ITOF | Integer to Float | |

| FPU | Floating Point | MADD.F | Multiply Add Float | |

| FPU | Floating Point | MSUB.F | Multiply Subtract Float | |

| FPU | Floating Point | MUL.F | Multiply Float | |

| FPU | Floating Point | Q31TOF | Fraction to Floating-point | |

| FPU | Floating Point | QSEED.F | Inverse Square Root Seed | |

| FPU | Floating Point | SUB.F | Subtract Float | |

| FPU | Floating Point | UPDFL | Update Flags | |

| FPU | Floating Point | UTOF | Unsigned to Floating-point |

Comparison with Other Microcontroller Architectures

In the automotive and industrial MCU landscape, Infineon’s TriCore™/AURIX™ architecture stands alongside other major architectures such as ARM Cortex-based microcontrollers, Power Architecture (PowerPC) based controllers, and more recently RISC-V based designs. Architecturally, TriCore’s™ niche is its unified MCU/DSP design and native multicore safety support. In contrast, many competitors historically used separate cores or accelerators for DSP tasks (for example, ARM’s Cortex-M4/M7 cores include a DSP instruction set, but earlier automotive designs often combined a CPU with a separate DSP or relied on fixed-function accelerators). TriCore™ was one of the first to meld DSP capabilities into a general-purpose controller core[9], giving it an edge in signal-processing-heavy automotive tasks like ignition control or motor control. Moreover, AURIX™ introduced multi-core lockstep and distributed memory protection at a time when many automotive MCU competitors were still single-core or dual-core. For instance, Texas Instruments’ Hercules safety microcontrollers use dual ARM Cortex-R4 cores in lockstep to achieve similar fault-detection as AURIX’s™ lockstep pairs, and NXP (Freescale)’s older PowerPC-based MCUs implemented lockstep on a single core pair. AURIX’s™ approach with up to three lockstep pairs (in a 2oo3 or 1oo2D configuration) on one chip was relatively unique, enabling higher ASIL-D performance within one device[10]. In terms of raw performance, TriCore™ cores at 300 MHz deliver comparable DMIPS/MHz to high-end ARM Cortex-R and Cortex-M cores. A 300 MHz TriCore™ 1.6.2 is roughly in the same class as a 300 MHz ARM Cortex-R5 or a 350 MHz Cortex-M7 in terms of Dhrystone performance, although specific benchmarks vary[11][12]. The AURIX TC3xx’s hexa-core design can outpace many dual- or triple-core competitors on aggregate throughput, though ARM-based families have also scaled up core counts in some SoC-like designs.

When comparing security features, Infineon’s decision to include a high-grade HSM on AURIX™ gave it a head start in automotive cybersecurity. ARM’s TrustZone technology (available on some Cortex-M35/M33 and higher cores) provides a form of security partitioning, but it’s not directly equivalent to a full HSM with its own CPU and crypto engine. Many automotive MCU vendors (like NXP and ST) have since incorporated dedicated security modules or accelerators in their ARM-based designs, but AURIX’s™ HSM (with EVITA High compliance) remains a standout for handling features like onboard encryption, secure boot, and even V2X cryptography without external chips[13]. On the other hand, the broader ecosystem for software and tools tends to favor ARM. ARM Cortex-based microcontrollers benefit from widespread compiler support, development tools, and a large developer community. Infineon’s TriCore™, being proprietary, has a more specialized toolchain (with commercial compilers from Tasking, HighTec, etc., and a smaller community), which can mean a higher barrier to entry for new developers. However, automotive Tier-1 suppliers have invested in TriCore™ toolchains for years, and Infineon provides AUTOSAR libraries and MCAL drivers that ease development in the automotive context[14].

In terms of industry adoption, TriCore™/AURIX™ has become one of the dominant architectures in European automotive electronics, often chosen for its safety and performance in powertrain and safety domains, while ARM-based microcontrollers have gained popularity especially in body electronics and new ECU designs due to their flexibility and the ARM ecosystem. Historically, high-end automotive MCUs were based on PowerPC cores (like NXP/Freescale MPC5xx/MPC55xx) or proprietary cores like Renesas V850/RH850. Infineon’s AURIX™ emerged as a strong competitor to these, offering a new option with multicore and DSP advantages. By the mid-2010s, ARM made inroads into this space (TI’s TMS570/Hercules with Cortex-R4, and later NXP and Renesas adopting ARM Cortex-R/M for some families), but many automotive OEMs continued to trust established platforms. A 2013 analysis noted that PowerPC was dominant, with Infineon’s TriCore™ and Renesas’s V850 as big competitors, and ARM as a “latest entrant” in the automotive MCU arena. Since then, ARM cores have seen increasing use in automotive for domains like gateways and ADAS (e.g., NVIDIA and Mobileye use ARM in their SoCs, and some microcontroller families like Cypress Traveo and NXP S32K are ARM-based), but AURIX™ maintains a significant share in high safety integrity applications.[15]

Looking forward, the rise of RISC-V open architecture presents both a competition and an opportunity. Infineon itself has announced that it will introduce a new AURIX™ family branch that includes RISC-V cores alongside TriCore™[16]. This reflects a trend toward heterogeneous architectures: pairing a proven safety-critical core (TriCore™) with supplementary cores that can be optimized for tasks like AI acceleration or network management. RISC-V’s open ecosystem could bring more developers and third-party IP into the fold, potentially addressing the ecosystem gap between TriCore™ and ARM. Other companies are also exploring RISC-V for automotive; for example, Western Digital and GreenWaves have automotive-oriented RISC-V processors, and some start-ups are aiming for ASIL-rated RISC-V cores. However, as of the TC3xx generation, AURIX’s™ competition remains largely the ARM Cortex-R5-based MCUs (like Renesas RH850/U2x series which moved to ARM cores, or NXP’s S32S which uses Cortex-R52) and the last of the line PowerPC-based units. In summary, AURIX’s™ TriCore™ architecture distinguishes itself with a laser focus on automotive needs – blending real-time control, DSP, built-in redundancy, and security in one package – whereas ARM architectures offer a broad general-purpose approach with wide support, and RISC-V is emerging as a flexible, open alternative. Each has its strengths: AURIX™ for integrated safety/security, ARM for its ubiquity and IP ecosystem, and RISC-V for customizability. Infineon’s strategy indicates a recognition that future architectures may combine these strengths to meet the ever-growing demands of software-defined vehicles[16].

See Also

External Links

- TriCore™ 1.3 Architecture Overview Handbook

- TriCore® TC1.3 & TC1.3.1 User Manual Volume 1 - Core Architecture

- TriCore® TC1.6P & TC1.6E User Manual Volume 1 - Core Architecture

- TriCore® TC1.6P & TC1.6E User Manual Volume 2 - Instruction Set

- TriCore™ TC1.6.2 User Manual Volume 1 - Core Architecture

- TriCore™ TC1.6.2 User Manual Volume 2 - Instruction Set

References

- ↑ 1.0 1.1 1.2 Welcome to the next generation AURIX™ TC4x, Thomas Boehm, Senior Vice President Automotive Microcontroller, 12 January 2022, https://www.infineon.com/dgdl/Infineon_AURIX_TC4x.pdf?fileId=8ac78c8b7e4b5364017e4e1a407c0001

- ↑ 2.0 2.1 History of TriCore™ - Infineon Technologies https://www.infineon.com/cms/en/product/promopages/historyoftricore/

- ↑ Safety Joins Performance: Infineon Introduces Automotive Multicore 32-bit Microcontroller Family AURIX™ to Meet Safety and Powertrain Requirements of Upcoming Vehicle Generations - Infineon Technologies https://www.infineon.com/cms/en/about-infineon/press/market-news/2012/INFATV201205-040.html

- ↑ Safety Microcontrollers: Texas Instruments Hercules vs Infineon AURIX https://www.linkedin.com/pulse/safety-microcontrollers-texas-instruments-hercules-vs-cook-meng-miet

- ↑ AURIX™ microcontroller TC3xx family of Infineon fuels automated driving and electromobility - Infineon Technologies https://www.infineon.com/cms/en/about-infineon/press/market-news/2016/INFATV201610-005.html

- ↑ 32-bit TriCore™ AURIX™– TC3xx - Infineon Technologies https://www.infineon.com/cms/en/product/microcontroller/32-bit-tricore-microcontroller/32-bit-tricore-aurix-tc3xx/

- ↑ UDE Debug, Trace and Test solutions for Infineon TriCore™ AURIX™ TC32, TC33, TC35, TC36, TC37, TC38, TC39, TC3x Microcontrollers https://www.pls-mc.com/products/infineon-tricore-aurix-tc32-tc33-tc35-tc36-tc37-tc38-tc39-microcontrollers/

- ↑ Infineon brings RISC-V to the automotive industry and is first to announce an automotive RISC-V microcontroller family – RISC-V International https://riscv.org/ecosystem-news/2025/03/infineon-brings-risc-v-to-the-automotive-industry-and-is-first-to-announce-an-automotive-risc-v-microcontroller-family/

- ↑ 32-bit TriCore™ AURIX™– TC3xx - Infineon Technologies https://www.infineon.com/cms/en/product/microcontroller/32-bit-tricore-microcontroller/32-bit-tricore-aurix-tc3xx/

- ↑ Safety Microcontrollers: Texas Instruments Hercules vs Infineon AURIX https://www.linkedin.com/pulse/safety-microcontrollers-texas-instruments-hercules-vs-cook-meng-miet

- ↑ Infineon AURIX - Wikipedia https://en.wikipedia.org/wiki/Infineon_AURIX

- ↑ Aurix TC3xx microcontroller - how to access shared variables from ... https://www.reddit.com/r/embedded/comments/10v8vtz/aurix_tc3xx_microcontroller_how_to_access_shared/

- ↑ UDE Debug, Trace and Test solutions for Infineon TriCore™ AURIX™ TC32, TC33, TC35, TC36, TC37, TC38, TC39, TC3x Microcontrollers https://www.pls-mc.com/products/infineon-tricore-aurix-tc32-tc33-tc35-tc36-tc37-tc38-tc39-microcontrollers/

- ↑ Infineon's AURIX™ & TRAVEO™ microcontroller families extend their support for IEC 61508 hardware and software metrics enabling industrial safety up to SIL-3 - Infineon Technologies https://www.infineon.com/cms/en/about-infineon/press/market-news/2023/INFATV202303-078.html

- ↑ Automotive world: PowerPC vs ARM vs V850 vs SH - Page 1 https://www.eevblog.com/forum/microcontrollers/automotive-world-powerpc-vs-arm-vs-v850-vs-sh/

- ↑ 16.0 16.1 Infineon brings RISC-V to the automotive industry and is first to announce an automotive RISC-V microcontroller family – RISC-V International https://riscv.org/ecosystem-news/2025/03/infineon-brings-risc-v-to-the-automotive-industry-and-is-first-to-announce-an-automotive-risc-v-microcontroller-family/